Difference between revisions of "Introducing jzIntv's Debugger"

(→Wrapping Up) |

|||

| Line 259: | Line 259: | ||

</CODE> | </CODE> | ||

The format of the memory dump is simple. At the left is the starting address. In the middle are hexadecimal values for 8 locations. At the right is an ASCII representation of the data. As you can see, starting on the second row at location $5028, the phrase " Copyright 2007 " is right where we expect it. The extra '.' characters between letters are due to the fact that memory locations are 16-bits wide, but characters are only 8 bits. Additional information could be in those other bits. | The format of the memory dump is simple. At the left is the starting address. In the middle are hexadecimal values for 8 locations. At the right is an ASCII representation of the data. As you can see, starting on the second row at location $5028, the phrase " Copyright 2007 " is right where we expect it. The extra '.' characters between letters are due to the fact that memory locations are 16-bits wide, but characters are only 8 bits. Additional information could be in those other bits. | ||

| + | |||

| + | = Stepping Through = | ||

| + | |||

| + | Now let's see what the whole program does. We'll first set a breakpoint at the last instruction, and then tell jzIntv to step to the end. | ||

| + | <CODE> | ||

| + | > b503b | ||

| + | Set breakpoint at $503B | ||

| + | > s | ||

| + | RD a=5022 d=0002 CP-1610 (PC = $5022) t=54475 | ||

| + | 0000 C0C0 0290 8007 5022 1E87 02f2 5023 ----I--- [[JSR]] R5,$503d 54479 | ||

| + | RD a=5023 d=0004 CP-1610 (PC = $5023) t=54479 | ||

| + | RD a=5024 d=0150 CP-1610 (PC = $5023) t=54479 | ||

| + | RD a=5025 d=003D CP-1610 (PC = $5023) t=54479 | ||

| + | 0000 C0C0 0290 8007 5022 5026 02f2 503D ----I-i- [[MVI@]] R5,R1 54491 | ||

| + | RD a=503D d=02A9 CP-1610 (PC = $503D) t=54491 | ||

| + | RD a=5026 d=0007 CP-1610 (PC = $503D) t=54491 | ||

| + | 0000 0007 0290 8007 5022 5027 02f2 503E ----I-i- [[MVI@]] R5,R4 54499 | ||

| + | RD a=503E d=02AC CP-1610 (PC = $503E) t=54499 | ||

| + | RD a=5027 d=02C9 CP-1610 (PC = $503E) t=54499 | ||

| + | 0000 0007 0290 8007 02C9 5028 02f2 503F ----I-i- [[B]] $5048 54507 | ||

| + | RD a=503F d=0200 CP-1610 (PC = $503F) t=54507 | ||

| + | RD a=5040 d=0007 CP-1610 (PC = $503F) t=54507 | ||

| + | 0000 0007 0290 8007 02C9 5028 02f2 5048 ----I-i- [[CLRC]] 54516 | ||

| + | RD a=5048 d=0006 CP-1610 (PC = $5048) t=54516 | ||

| + | 0000 0007 0290 8007 02C9 5028 02f2 5049 ----I--- [[SLL]] R1 54520 | ||

| + | RD a=5049 d=0049 CP-1610 (PC = $5049) t=54520 | ||

| + | 0000 000E 0290 8007 02C9 5028 02f2 504A ----I--- [[RRC]] R1 54526 | ||

| + | RD a=504A d=0071 CP-1610 (PC = $504A) t=54526 | ||

| + | 0000 0007 0290 8007 02C9 5028 02f2 504B ----I--- [[B]] $5053 54532 | ||

| + | RD a=504B d=0200 CP-1610 (PC = $504B) t=54532 | ||

| + | RD a=504C d=0006 CP-1610 (PC = $504B) t=54532 | ||

| + | 0000 0007 0290 8007 02C9 5028 02f2 5053 ----I-i- [[MVI@]] R5,R0 54541 | ||

| + | RD a=5053 d=02A8 CP-1610 (PC = $5053) t=54541 | ||

| + | RD a=5028 d=0020 CP-1610 (PC = $5053) t=54541 | ||

| + | 0020 0007 0290 8007 02C9 5029 02f2 5054 ----I-i- [[TSTR]] R0 54549 | ||

| + | RD a=5054 d=0080 CP-1610 (PC = $5054) t=54549 | ||

| + | 0020 0007 0290 8007 02C9 5029 02f2 5055 ----I-i- [[BNEQ]] $504d 54555 | ||

| + | RD a=5055 d=022C CP-1610 (PC = $5055) t=54555 | ||

| + | RD a=5056 d=0009 CP-1610 (PC = $5055) t=54555 | ||

| + | 0020 0007 0290 8007 02C9 5029 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54564 | ||

| + | RD a=504D d=0338 CP-1610 (PC = $504D) t=54564 | ||

| + | RD a=504E d=0020 CP-1610 (PC = $504D) t=54564 | ||

| + | 0000 0007 0290 8007 02C9 5029 02f2 504F -C-ZI-i- [[SLL]] R0,2 54572 | ||

| + | RD a=504F d=004C CP-1610 (PC = $504F) t=54572 | ||

| + | 0000 0007 0290 8007 02C9 5029 02f2 5050 -C-ZI--- [[SLL]] R0 54580 | ||

| + | RD a=5050 d=0048 CP-1610 (PC = $5050) t=54580 | ||

| + | 0000 0007 0290 8007 02C9 5029 02f2 5051 -C-ZI--- [[ADDR]] R1,R0 54586 | ||

| + | RD a=5051 d=00C8 CP-1610 (PC = $5051) t=54586 | ||

| + | 0007 0007 0290 8007 02C9 5029 02f2 5052 ----I-i- [[MVO@]] R0,R4 54592 | ||

| + | RD a=5052 d=0260 CP-1610 (PC = $5052) t=54592 | ||

| + | WR a=02C9 d=0007 CP-1610 (PC = $5052) t=54592 | ||

| + | 0007 0007 0290 8007 02CA 5029 02f2 5053 ----I--- [[MVI@]] R5,R0 54601 | ||

| + | RD a=5029 d=0020 CP-1610 (PC = $5053) t=54601 | ||

| + | 0020 0007 0290 8007 02CA 502A 02f2 5054 ----I-i- [[TSTR]] R0 54609 | ||

| + | 0020 0007 0290 8007 02CA 502A 02f2 5055 ----I-i- [[BNEQ]] $504d 54615 | ||

| + | 0020 0007 0290 8007 02CA 502A 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54624 | ||

| + | 0000 0007 0290 8007 02CA 502A 02f2 504F -C-ZI-i- [[SLL]] R0,2 54632 | ||

| + | 0000 0007 0290 8007 02CA 502A 02f2 5050 -C-ZI--- [[SLL]] R0 54640 | ||

| + | 0000 0007 0290 8007 02CA 502A 02f2 5051 -C-ZI--- [[ADDR]] R1,R0 54646 | ||

| + | 0007 0007 0290 8007 02CA 502A 02f2 5052 ----I-i- [[MVO@]] R0,R4 54652 | ||

| + | WR a=02CA d=0007 CP-1610 (PC = $5052) t=54652 | ||

| + | 0007 0007 0290 8007 02CB 502A 02f2 5053 ----I--- [[MVI@]] R5,R0 54661 | ||

| + | RD a=502A d=0043 CP-1610 (PC = $5053) t=54661 | ||

| + | 0043 0007 0290 8007 02CB 502B 02f2 5054 ----I-i- [[TSTR]] R0 54669 | ||

| + | 0043 0007 0290 8007 02CB 502B 02f2 5055 ----I-i- [[BNEQ]] $504d 54675 | ||

| + | 0043 0007 0290 8007 02CB 502B 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54684 | ||

| + | 0023 0007 0290 8007 02CB 502B 02f2 504F -C--I-i- [[SLL]] R0,2 54692 | ||

| + | 008C 0007 0290 8007 02CB 502B 02f2 5050 -C--I--- [[SLL]] R0 54700 | ||

| + | 0118 0007 0290 8007 02CB 502B 02f2 5051 -C--I--- [[ADDR]] R1,R0 54706 | ||

| + | 011F 0007 0290 8007 02CB 502B 02f2 5052 ----I-i- [[MVO@]] R0,R4 54712 | ||

| + | WR a=02CB d=011F CP-1610 (PC = $5052) t=54712 | ||

| + | 011F 0007 0290 8007 02CC 502B 02f2 5053 ----I--- [[MVI@]] R5,R0 54721 | ||

| + | RD a=502B d=006F CP-1610 (PC = $5053) t=54721 | ||

| + | 006F 0007 0290 8007 02CC 502C 02f2 5054 ----I-i- [[TSTR]] R0 54729 | ||

| + | 006F 0007 0290 8007 02CC 502C 02f2 5055 ----I-i- [[BNEQ]] $504d 54735 | ||

| + | 006F 0007 0290 8007 02CC 502C 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54744 | ||

| + | 004F 0007 0290 8007 02CC 502C 02f2 504F -C--I-i- [[SLL]] R0,2 54752 | ||

| + | 013C 0007 0290 8007 02CC 502C 02f2 5050 -C--I--- [[SLL]] R0 54760 | ||

| + | 0278 0007 0290 8007 02CC 502C 02f2 5051 -C--I--- [[ADDR]] R1,R0 54766 | ||

| + | 027F 0007 0290 8007 02CC 502C 02f2 5052 ----I-i- [[MVO@]] R0,R4 54772 | ||

| + | WR a=02CC d=027F CP-1610 (PC = $5052) t=54772 | ||

| + | 027F 0007 0290 8007 02CD 502C 02f2 5053 ----I--- [[MVI@]] R5,R0 54781 | ||

| + | RD a=502C d=0070 CP-1610 (PC = $5053) t=54781 | ||

| + | 0070 0007 0290 8007 02CD 502D 02f2 5054 ----I-i- [[TSTR]] R0 54789 | ||

| + | 0070 0007 0290 8007 02CD 502D 02f2 5055 ----I-i- [[BNEQ]] $504d 54795 | ||

| + | 0070 0007 0290 8007 02CD 502D 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54804 | ||

| + | 0050 0007 0290 8007 02CD 502D 02f2 504F -C--I-i- [[SLL]] R0,2 54812 | ||

| + | 0140 0007 0290 8007 02CD 502D 02f2 5050 -C--I--- [[SLL]] R0 54820 | ||

| + | 0280 0007 0290 8007 02CD 502D 02f2 5051 -C--I--- [[ADDR]] R1,R0 54826 | ||

| + | 0287 0007 0290 8007 02CD 502D 02f2 5052 ----I-i- [[MVO@]] R0,R4 54832 | ||

| + | WR a=02CD d=0287 CP-1610 (PC = $5052) t=54832 | ||

| + | 0287 0007 0290 8007 02CE 502D 02f2 5053 ----I--- [[MVI@]] R5,R0 54841 | ||

| + | RD a=502D d=0079 CP-1610 (PC = $5053) t=54841 | ||

| + | 0079 0007 0290 8007 02CE 502E 02f2 5054 ----I-i- [[TSTR]] R0 54849 | ||

| + | 0079 0007 0290 8007 02CE 502E 02f2 5055 ----I-i- [[BNEQ]] $504d 54855 | ||

| + | 0079 0007 0290 8007 02CE 502E 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54864 | ||

| + | 0059 0007 0290 8007 02CE 502E 02f2 504F -C--I-i- [[SLL]] R0,2 54872 | ||

| + | 0164 0007 0290 8007 02CE 502E 02f2 5050 -C--I--- [[SLL]] R0 54880 | ||

| + | 02C8 0007 0290 8007 02CE 502E 02f2 5051 -C--I--- [[ADDR]] R1,R0 54886 | ||

| + | 02CF 0007 0290 8007 02CE 502E 02f2 5052 ----I-i- [[MVO@]] R0,R4 54892 | ||

| + | WR a=02CE d=02CF CP-1610 (PC = $5052) t=54892 | ||

| + | 02CF 0007 0290 8007 02CF 502E 02f2 5053 ----I--- [[MVI@]] R5,R0 54901 | ||

| + | RD a=502E d=0072 CP-1610 (PC = $5053) t=54901 | ||

| + | 0072 0007 0290 8007 02CF 502F 02f2 5054 ----I-i- [[TSTR]] R0 54909 | ||

| + | 0072 0007 0290 8007 02CF 502F 02f2 5055 ----I-i- [[BNEQ]] $504d 54915 | ||

| + | 0072 0007 0290 8007 02CF 502F 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54924 | ||

| + | 0052 0007 0290 8007 02CF 502F 02f2 504F -C--I-i- [[SLL]] R0,2 54932 | ||

| + | 0148 0007 0290 8007 02CF 502F 02f2 5050 -C--I--- [[SLL]] R0 54940 | ||

| + | 0290 0007 0290 8007 02CF 502F 02f2 5051 -C--I--- [[ADDR]] R1,R0 54946 | ||

| + | 0297 0007 0290 8007 02CF 502F 02f2 5052 ----I-i- [[MVO@]] R0,R4 54952 | ||

| + | WR a=02CF d=0297 CP-1610 (PC = $5052) t=54952 | ||

| + | 0297 0007 0290 8007 02D0 502F 02f2 5053 ----I--- [[MVI@]] R5,R0 54961 | ||

| + | RD a=502F d=0069 CP-1610 (PC = $5053) t=54961 | ||

| + | 0069 0007 0290 8007 02D0 5030 02f2 5054 ----I-i- [[TSTR]] R0 54969 | ||

| + | 0069 0007 0290 8007 02D0 5030 02f2 5055 ----I-i- [[BNEQ]] $504d 54975 | ||

| + | 0069 0007 0290 8007 02D0 5030 02f2 504D ----I-i- [[SUBI]] #$0020,R0 54984 | ||

| + | 0049 0007 0290 8007 02D0 5030 02f2 504F -C--I-i- [[SLL]] R0,2 54992 | ||

| + | 0124 0007 0290 8007 02D0 5030 02f2 5050 -C--I--- [[SLL]] R0 55000 | ||

| + | 0248 0007 0290 8007 02D0 5030 02f2 5051 -C--I--- [[ADDR]] R1,R0 55006 | ||

| + | 024F 0007 0290 8007 02D0 5030 02f2 5052 ----I-i- [[MVO@]] R0,R4 55012 | ||

| + | WR a=02D0 d=024F CP-1610 (PC = $5052) t=55012 | ||

| + | 024F 0007 0290 8007 02D1 5030 02f2 5053 ----I--- [[MVI@]] R5,R0 55021 | ||

| + | RD a=5030 d=0067 CP-1610 (PC = $5053) t=55021 | ||

| + | 0067 0007 0290 8007 02D1 5031 02f2 5054 ----I-i- [[TSTR]] R0 55029 | ||

| + | 0067 0007 0290 8007 02D1 5031 02f2 5055 ----I-i- [[BNEQ]] $504d 55035 | ||

| + | 0067 0007 0290 8007 02D1 5031 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55044 | ||

| + | 0047 0007 0290 8007 02D1 5031 02f2 504F -C--I-i- [[SLL]] R0,2 55052 | ||

| + | 011C 0007 0290 8007 02D1 5031 02f2 5050 -C--I--- [[SLL]] R0 55060 | ||

| + | 0238 0007 0290 8007 02D1 5031 02f2 5051 -C--I--- [[ADDR]] R1,R0 55066 | ||

| + | 023F 0007 0290 8007 02D1 5031 02f2 5052 ----I-i- [[MVO@]] R0,R4 55072 | ||

| + | WR a=02D1 d=023F CP-1610 (PC = $5052) t=55072 | ||

| + | 023F 0007 0290 8007 02D2 5031 02f2 5053 ----I--- [[MVI@]] R5,R0 55081 | ||

| + | RD a=5031 d=0068 CP-1610 (PC = $5053) t=55081 | ||

| + | 0068 0007 0290 8007 02D2 5032 02f2 5054 ----I-i- [[TSTR]] R0 55089 | ||

| + | 0068 0007 0290 8007 02D2 5032 02f2 5055 ----I-i- [[BNEQ]] $504d 55095 | ||

| + | 0068 0007 0290 8007 02D2 5032 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55104 | ||

| + | 0048 0007 0290 8007 02D2 5032 02f2 504F -C--I-i- [[SLL]] R0,2 55112 | ||

| + | 0120 0007 0290 8007 02D2 5032 02f2 5050 -C--I--- [[SLL]] R0 55120 | ||

| + | 0240 0007 0290 8007 02D2 5032 02f2 5051 -C--I--- [[ADDR]] R1,R0 55126 | ||

| + | 0247 0007 0290 8007 02D2 5032 02f2 5052 ----I-i- [[MVO@]] R0,R4 55132 | ||

| + | WR a=02D2 d=0247 CP-1610 (PC = $5052) t=55132 | ||

| + | 0247 0007 0290 8007 02D3 5032 02f2 5053 ----I--- [[MVI@]] R5,R0 55141 | ||

| + | RD a=5032 d=0074 CP-1610 (PC = $5053) t=55141 | ||

| + | 0074 0007 0290 8007 02D3 5033 02f2 5054 ----I-i- [[TSTR]] R0 55149 | ||

| + | 0074 0007 0290 8007 02D3 5033 02f2 5055 ----I-i- [[BNEQ]] $504d 55155 | ||

| + | 0074 0007 0290 8007 02D3 5033 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55164 | ||

| + | 0054 0007 0290 8007 02D3 5033 02f2 504F -C--I-i- [[SLL]] R0,2 55172 | ||

| + | 0150 0007 0290 8007 02D3 5033 02f2 5050 -C--I--- [[SLL]] R0 55180 | ||

| + | 02A0 0007 0290 8007 02D3 5033 02f2 5051 -C--I--- [[ADDR]] R1,R0 55186 | ||

| + | 02A7 0007 0290 8007 02D3 5033 02f2 5052 ----I-i- [[MVO@]] R0,R4 55192 | ||

| + | WR a=02D3 d=02A7 CP-1610 (PC = $5052) t=55192 | ||

| + | 02A7 0007 0290 8007 02D4 5033 02f2 5053 ----I--- [[MVI@]] R5,R0 55201 | ||

| + | RD a=5033 d=0020 CP-1610 (PC = $5053) t=55201 | ||

| + | 0020 0007 0290 8007 02D4 5034 02f2 5054 ----I-i- [[TSTR]] R0 55209 | ||

| + | 0020 0007 0290 8007 02D4 5034 02f2 5055 ----I-i- [[BNEQ]] $504d 55215 | ||

| + | 0020 0007 0290 8007 02D4 5034 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55224 | ||

| + | 0000 0007 0290 8007 02D4 5034 02f2 504F -C-ZI-i- [[SLL]] R0,2 55232 | ||

| + | 0000 0007 0290 8007 02D4 5034 02f2 5050 -C-ZI--- [[SLL]] R0 55240 | ||

| + | 0000 0007 0290 8007 02D4 5034 02f2 5051 -C-ZI--- [[ADDR]] R1,R0 55246 | ||

| + | 0007 0007 0290 8007 02D4 5034 02f2 5052 ----I-i- [[MVO@]] R0,R4 55252 | ||

| + | WR a=02D4 d=0007 CP-1610 (PC = $5052) t=55252 | ||

| + | 0007 0007 0290 8007 02D5 5034 02f2 5053 ----I--- [[MVI@]] R5,R0 55261 | ||

| + | RD a=5034 d=0032 CP-1610 (PC = $5053) t=55261 | ||

| + | 0032 0007 0290 8007 02D5 5035 02f2 5054 ----I-i- [[TSTR]] R0 55269 | ||

| + | 0032 0007 0290 8007 02D5 5035 02f2 5055 ----I-i- [[BNEQ]] $504d 55275 | ||

| + | 0032 0007 0290 8007 02D5 5035 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55284 | ||

| + | 0012 0007 0290 8007 02D5 5035 02f2 504F -C--I-i- [[SLL]] R0,2 55292 | ||

| + | 0048 0007 0290 8007 02D5 5035 02f2 5050 -C--I--- [[SLL]] R0 55300 | ||

| + | 0090 0007 0290 8007 02D5 5035 02f2 5051 -C--I--- [[ADDR]] R1,R0 55306 | ||

| + | 0097 0007 0290 8007 02D5 5035 02f2 5052 ----I-i- [[MVO@]] R0,R4 55312 | ||

| + | WR a=02D5 d=0097 CP-1610 (PC = $5052) t=55312 | ||

| + | 0097 0007 0290 8007 02D6 5035 02f2 5053 ----I--- [[MVI@]] R5,R0 55321 | ||

| + | RD a=5035 d=0030 CP-1610 (PC = $5053) t=55321 | ||

| + | 0030 0007 0290 8007 02D6 5036 02f2 5054 ----I-i- [[TSTR]] R0 55329 | ||

| + | 0030 0007 0290 8007 02D6 5036 02f2 5055 ----I-i- [[BNEQ]] $504d 55335 | ||

| + | 0030 0007 0290 8007 02D6 5036 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55344 | ||

| + | 0010 0007 0290 8007 02D6 5036 02f2 504F -C--I-i- [[SLL]] R0,2 55352 | ||

| + | 0040 0007 0290 8007 02D6 5036 02f2 5050 -C--I--- [[SLL]] R0 55360 | ||

| + | 0080 0007 0290 8007 02D6 5036 02f2 5051 -C--I--- [[ADDR]] R1,R0 55366 | ||

| + | 0087 0007 0290 8007 02D6 5036 02f2 5052 ----I-i- [[MVO@]] R0,R4 55372 | ||

| + | WR a=02D6 d=0087 CP-1610 (PC = $5052) t=55372 | ||

| + | 0087 0007 0290 8007 02D7 5036 02f2 5053 ----I--- [[MVI@]] R5,R0 55381 | ||

| + | RD a=5036 d=0030 CP-1610 (PC = $5053) t=55381 | ||

| + | 0030 0007 0290 8007 02D7 5037 02f2 5054 ----I-i- [[TSTR]] R0 55389 | ||

| + | 0030 0007 0290 8007 02D7 5037 02f2 5055 ----I-i- [[BNEQ]] $504d 55395 | ||

| + | 0030 0007 0290 8007 02D7 5037 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55404 | ||

| + | 0010 0007 0290 8007 02D7 5037 02f2 504F -C--I-i- [[SLL]] R0,2 55412 | ||

| + | 0040 0007 0290 8007 02D7 5037 02f2 5050 -C--I--- [[SLL]] R0 55420 | ||

| + | 0080 0007 0290 8007 02D7 5037 02f2 5051 -C--I--- [[ADDR]] R1,R0 55426 | ||

| + | 0087 0007 0290 8007 02D7 5037 02f2 5052 ----I-i- [[MVO@]] R0,R4 55432 | ||

| + | WR a=02D7 d=0087 CP-1610 (PC = $5052) t=55432 | ||

| + | 0087 0007 0290 8007 02D8 5037 02f2 5053 ----I--- [[MVI@]] R5,R0 55441 | ||

| + | RD a=5037 d=0037 CP-1610 (PC = $5053) t=55441 | ||

| + | 0037 0007 0290 8007 02D8 5038 02f2 5054 ----I-i- [[TSTR]] R0 55449 | ||

| + | 0037 0007 0290 8007 02D8 5038 02f2 5055 ----I-i- [[BNEQ]] $504d 55455 | ||

| + | 0037 0007 0290 8007 02D8 5038 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55464 | ||

| + | 0017 0007 0290 8007 02D8 5038 02f2 504F -C--I-i- [[SLL]] R0,2 55472 | ||

| + | 005C 0007 0290 8007 02D8 5038 02f2 5050 -C--I--- [[SLL]] R0 55480 | ||

| + | 00B8 0007 0290 8007 02D8 5038 02f2 5051 -C--I--- [[ADDR]] R1,R0 55486 | ||

| + | 00BF 0007 0290 8007 02D8 5038 02f2 5052 ----I-i- [[MVO@]] R0,R4 55492 | ||

| + | WR a=02D8 d=00BF CP-1610 (PC = $5052) t=55492 | ||

| + | 00BF 0007 0290 8007 02D9 5038 02f2 5053 ----I--- [[MVI@]] R5,R0 55501 | ||

| + | RD a=5038 d=0020 CP-1610 (PC = $5053) t=55501 | ||

| + | 0020 0007 0290 8007 02D9 5039 02f2 5054 ----I-i- [[TSTR]] R0 55509 | ||

| + | 0020 0007 0290 8007 02D9 5039 02f2 5055 ----I-i- [[BNEQ]] $504d 55515 | ||

| + | 0020 0007 0290 8007 02D9 5039 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55524 | ||

| + | 0000 0007 0290 8007 02D9 5039 02f2 504F -C-ZI-i- [[SLL]] R0,2 55532 | ||

| + | 0000 0007 0290 8007 02D9 5039 02f2 5050 -C-ZI--- [[SLL]] R0 55540 | ||

| + | 0000 0007 0290 8007 02D9 5039 02f2 5051 -C-ZI--- [[ADDR]] R1,R0 55546 | ||

| + | 0007 0007 0290 8007 02D9 5039 02f2 5052 ----I-i- [[MVO@]] R0,R4 55552 | ||

| + | WR a=02D9 d=0007 CP-1610 (PC = $5052) t=55552 | ||

| + | 0007 0007 0290 8007 02DA 5039 02f2 5053 ----I--- [[MVI@]] R5,R0 55561 | ||

| + | RD a=5039 d=0020 CP-1610 (PC = $5053) t=55561 | ||

| + | 0020 0007 0290 8007 02DA 503A 02f2 5054 ----I-i- [[TSTR]] R0 55569 | ||

| + | 0020 0007 0290 8007 02DA 503A 02f2 5055 ----I-i- [[BNEQ]] $504d 55575 | ||

| + | 0020 0007 0290 8007 02DA 503A 02f2 504D ----I-i- [[SUBI]] #$0020,R0 55584 | ||

| + | 0000 0007 0290 8007 02DA 503A 02f2 504F -C-ZI-i- [[SLL]] R0,2 55592 | ||

| + | 0000 0007 0290 8007 02DA 503A 02f2 5050 -C-ZI--- [[SLL]] R0 55600 | ||

| + | 0000 0007 0290 8007 02DA 503A 02f2 5051 -C-ZI--- [[ADDR]] R1,R0 55606 | ||

| + | 0007 0007 0290 8007 02DA 503A 02f2 5052 ----I-i- [[MVO@]] R0,R4 55612 | ||

| + | WR a=02DA d=0007 CP-1610 (PC = $5052) t=55612 | ||

| + | 0007 0007 0290 8007 02DB 503A 02f2 5053 ----I--- [[MVI@]] R5,R0 55621 | ||

| + | RD a=503A d=0000 CP-1610 (PC = $5053) t=55621 | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 5054 ----I-i- [[TSTR]] R0 55629 | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 5055 ---ZI-i- [[BNEQ]] $504d 55635 | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 5057 ---ZI-i- [[SLL]]C R1 55642 | ||

| + | RD a=5057 d=0059 CP-1610 (PC = $5057) t=55642 | ||

| + | 0000 000E 0290 8007 02DB 503B 02f2 5058 ----I--- [[ADCR]] R0 55648 | ||

| + | RD a=5058 d=0028 CP-1610 (PC = $5058) t=55648 | ||

| + | 0000 000E 0290 8007 02DB 503B 02f2 5059 ---ZI-i- [[SLR]] R1 55654 | ||

| + | RD a=5059 d=0061 CP-1610 (PC = $5059) t=55654 | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 505A ----I--- [[ADDR]] R0,R7 55660 | ||

| + | RD a=505A d=00C7 CP-1610 (PC = $505A) t=55660 | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 505B ----I-i- [[MOVR]] R5,R7 55667 | ||

| + | RD a=505B d=00AF CP-1610 (PC = $505B) t=55667 | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 503B ----I-i- [[B]] $503b 55674 | ||

| + | Hit breakpoint at $503B | ||

| + | 0000 0007 0290 8007 02DB 503B 02f2 503B ----I-i- [[B]] $503b 55674 | ||

| + | > | ||

| + | </CODE> | ||

| + | |||

= Wrapping Up = | = Wrapping Up = | ||

| − | That concludes the quick tour of the most useful commands in jzIntv's debugger. You're encouraged at this point to try single-stepping through | + | That concludes the quick tour of the most useful commands in jzIntv's debugger. You can quit the debugger by giving it the "Q" command. You're encouraged at this point to try single-stepping through other programs to see how the instructions work. The next tutorial aims at introducing the various families of instructions. |

Revision as of 02:36, 8 October 2007

jzIntv offers a simple command-line oriented debugger. It should be familiar in style to anyone who has used the Apple ][ Monitor or DOS's DEBUG.EXE.

Contents

Invoking the Debugger

To invoke the debugger, add the "-d" flag to jzIntv's command line. For example, using "hello2.rom" from the Hello World Tutorial:

jzintv -d hello2.rom

This will invoke jzIntv, and present you with a prompt:

Loading:

hello2.rom

jzintv: Initializing Master Component and peripherals...

gfx: Searching for video modes near 320x200x8 with:

gfx: Hardware surf, Double buf, Sync blit, Software pal, Windowed

gfx: Selected: 320x200x8 with:

gfx: Software surf, Single buf, Sync blit, Hardware pal, Windowed

snd: buf_size: wanted 2048, got 2048

ay8910: Automatic sliding-window setting: 10

CP-1610 [0x0000...0x0000]

PSG0 AY8914 [0x01F0...0x01FF]

[Graphics] [0x0000...0x0000]

[Sound] [0x0000...0x0000]

Scratch RAM [0x0100...0x01EF]

System RAM [0x0200...0x035F]

EXEC ROM [0x1000...0x1FFF]

Pad Pair 0 [0x01F0...0x01FF]

STIC [0x0000...0x007F]

STIC [0x4000...0x403F]

STIC [0x8000...0x803F]

STIC [0xC000...0xC03F]

STIC (BTAB) [0x0200...0x02EF]

STIC (GRAM) [0x3000...0x3FFF]

[Event] [0x0000...0x0000]

[Rate Ctrl] [0x0000...0x0000]

ICart [R ] [0x5000...0x50FF]

CP-1610 Snoop [0x0200...0x035F]

[Debugger] [0x0000...0xFFFF]

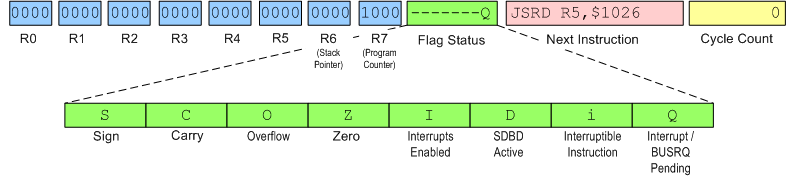

0000 0000 0000 0000 0000 0000 0000 1000 -------Q JSRD R5,$1026 0

>

Most of this output is jzIntv's initialization. The last portion is the debugger prompt.

The Debugger Prompt

0000 0000 0000 0000 0000 0000 0000 1000 -------Q JSRD R5,$1026 0

>

The prompt shown above is the debugger's input prompt. From here, you can tell the debugger what to do next. Before each prompt, jzIntv reports specific information about the state of the machine. The following diagram illustrates:

R0 through R7 are the CPU's 8 registers. Each register is 16 bits wide. jzIntv's debugger shows their values in hexadecimal.

The "flags" field shows what CPU flags are currently set. jzIntv tracks 8 separate flags:

| S | Sign Flag |

| C | Carry Flag |

| O | Overflow Flag |

| Z | Zero Flag |

| I | Interrupt Enable Flag |

| D | Double Byte Data Flag |

| i | Previous instruction was interruptible |

When a flag is set, jzIntv shows the letter for that flag. When the flag is clear, jzIntv shows a dash. This makes it easy to see what flags are currently set, without having to remember their exact order. The last flag position is special. It shows the current interrupt status:

| q | Interrupt asserted |

| b | BUSRQ asserted |

| Q | Interrupt being taken |

| B | CPU halted by BUSRQ |

In the example above, jzIntv shows the CPU as taking an interrupt. Really, it's coming out of reset, which is similar. Don't worry too much about interrupts for the moment.

Introducing the Registers

The CPU's registers act as a scratch pad, holding values for instructions to operate on. Some registers have special purposes. All the registers can be used for general purpose computation. Here's a quick reference to what each register can be used for.

| Register | General Purpose | Shift Instructions | Indirect Pointer | Return Address |

|---|---|---|---|---|

| R0 | X | X | ||

| R1 | X | X | X | |

| R2 | X | X | X | |

| R3 | X | X | X | |

| R4 | X | Auto-increment | X | |

| R5 | X | Auto-increment | X | |

| R6 | X | Stack | X | |

| R7 | * | Program Counter |

R6 and R7 are special. R6 is the stack pointer. R7 is the program counter. The assembler accepts SP and PC as aliases for R6 and R7. You can perform arbitrary arithmetic on either, although performing math on the program counter usually is a bad idea unless you really know what you're doing.

You will want to pay attention to R7 to know where you are at in your program. You can use the listing file, as described in the Hello World tutorial to relate what you wrote to what the debugger shows you.

Debugger Commands

The debugger offers a series of single-letter commands. You can find a full summary here. For this tutorial, we will focus on a small subset of these.

| Command | Description |

|---|---|

R <#> | Run for <#> cycles. If no argument given, runs "forever" |

S <#> | Step for <#> cycles. If no argument given, steps "forever" |

B <#> | set Breakpoint at location <#> |

M <A> <B> | show Memory at location <A>. Show at least <B> locations. |

U <A> <B> | Unassemble memory at location <A>. Show at least <B> instrs. |

Q | Quit jzIntv |

The commands are case-insensitive. That is, "R 100" (run 100 instructions) is the same as "r 100". The debugger also offers a short-cut: Pressing enter alone on a line is the same as "s 1". That is, it steps a single instruction.

First Steps: Watching Things Happen

Start the debugger using "hello2.rom" from the Hello World Tutorial's Example 2:

jzintv -d hello2.rom

Once at the debugger prompt, press [Enter] a couple of times. You should see output similar to the following:

0000 0000 0000 0000 0000 0000 0000 1000 -------- JSRD R5,$1026 0 > Starting jzIntv... RD a=1000 d=0004 CP-1610 (PC = $1000) t=0 RD a=1001 d=0112 CP-1610 (PC = $1000) t=0 RD a=1002 d=0026 CP-1610 (PC = $1000) t=0 0000 0000 0000 0000 0000 1003 0000 1026 -------- MVII #$02f1,R6 12 > RD a=1026 d=02BE CP-1610 (PC = $1026) t=12 RD a=1027 d=02F1 CP-1610 (PC = $1026) t=12 0000 0000 0000 0000 0000 1003 02f1 1028 ------i- JSR R5,$1a83 21 > RD a=1028 d=0004 CP-1610 (PC = $1028) t=21 RD a=1029 d=0118 CP-1610 (PC = $1028) t=21 RD a=102A d=0283 CP-1610 (PC = $1028) t=21 0000 0000 0000 0000 0000 102B 02f1 1A83 ------i- PSHR R5 33 > RD a=1A83 d=0275 CP-1610 (PC = $1A83) t=33 WR a=02F1 d=102B CP-1610 (PC = $1A83) t=33 0000 0000 0000 0000 0000 102B 02f2 1A84 -------- PSHR R0 42 >

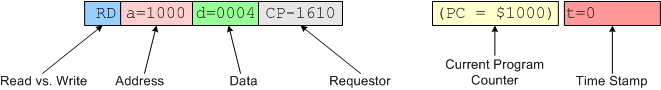

As you can see, jzIntv shows you the current status and the next instruction it will execute at each prompt. As each instruction executes, it also outputs memory transactions as they go by. This allows you to watch what the CPU is reading or writing. The following diagram illustrates how to interpret each of these lines.

These lines show you every read and write the CPU makes. The debugger normally suppresses these unless you step through code as we have above.

In this particular code sequence, we can see the EXEC begin to initialize itself. First, it jumps from the start of ROM to the first real bit of code. Then it sets up the stack pointer, and jumps to yet another subroutine. Notice how the register values, particularly the program counter (R7), stack pointer (R6) and return address (R5) change values. Click on the instructions themselves to get a description of what each one does.

Running Ahead to Our Code

At this point, it would be useful to jump ahead to our own program code. The simulated Intellivision needs to run the EXEC code that leads up our program, but we want the simulation to stop at the first instruction of our code. We accomplish this with a breakpoint.

Take a look at hello2.lst from the Hello World's example 2. Below is just the first portion:

00005000 ROMHDR 0000500d ZERO

00005022 MAIN 0000500f ONES

00005014 TITLE 0000503d PRINT.FLS

0000503b here 0000503d PRINT

0000503e PRINT.LS 00005048 PRINT.S

00005041 PRINT.FLP 00005042 PRINT.LP

00005043 PRINT.P 00005044 PRINT.R

00005053 PRINT.1st 0000504d PRINT.tloop

� ROMW 16

0x5000 ORG $5000

;------------------------------------------------------------------------------

; EXEC-friendly ROM header.

;------------------------------------------------------------------------------

5000 000d 0050 ROMHDR: BIDECLE ZERO ; MOB picture base (points to NULL list)

5002 000d 0050 BIDECLE ZERO ; Process table (points to NULL list)

5004 0022 0050 BIDECLE MAIN ; Program start address

5006 000d 0050 BIDECLE ZERO ; Bkgnd picture base (points to NULL list)

5008 000f 0050 BIDECLE ONES ; GRAM pictures (points to NULL list)

500a 0014 0050 BIDECLE TITLE ; Cartridge title/date

500c 03c0 DECLE $03C0 ; Flags: No ECS title, run code after title,

; ... no clicks

500d 0000 ZERO: DECLE $0000 ; Screen border control

500e 0000 DECLE $0000 ; 0 = color stack, 1 = f/b mode

500f 0001 0001 0001 ONES: DECLE 1, 1, 1, 1, 1 ; Color stack initialization

5012 0001 0001

;------------------------------------------------------------------------------

5014 006b 0048 0065 TITLE DECLE 107, "Hello World!", 0

5017 006c 006c 006f 0020 0057 006f 0072 006c

501f 0064 0021 0000

5022 0002 MAIN EIS ; Enable interrupts

5023 0004 0150 003d CALL PRINT.FLS

5026 0007 DECLE 7 ; 7 is the color number for "white"

5027 02c9 DECLE $200 + 10*20 + 1

5028 0020 0020 0043 DECLE " Copyright 2007 ", 0

502b 006f 0070 0079 0072 0069 0067 0068 0074

5033 0020 0032 0030 0030 0037 0020 0020 0000

503b 0220 0001 here B here ; Spin forever.

From this, you can see that the first instruction (the "EIS" instruction) is at location $5022. Use the "B" command to set a breakpoint here, and the "R" command to tell jzintv to run. jzIntv will stop when it reaches the breakpoint. The boldface portions below illustrate the commands you should type:

0000 0000 0000 0000 0000 102B 02f2 1A84 -------- PSHR R0 42 > b 5022 Set breakpoint at $5022 > r Hit breakpoint at $5022 0000 C0C0 0290 8007 5022 1E87 02f2 5022 ------i- EIS 54475 >

Pulling It Apart: Disassembly and Dumping

Now we can look ahead at the next couple of instructions that will execute. The "U" command will Unassemble the next several instructions. "U" by itself starts at the current instruction and outputs the next several:

> u

$5022: 0002 EIS

$5023: 0004 0150 003d JSR R5,$503d

$5026: 0007 SETC

$5027: 02c9 ADD@ R1,R1

$5028: 0020 NEGR R0

$5029: 0020 NEGR R0

$502A: 0043 SWAP R3

$502B: 006f SAR R3,2

$502C: 0070 RRC R0

$502D: 0079 SARC R1

$502E: 0072 RRC R2

$502F: 0069 SAR R1

$5030: 0067 SLR R3,2

$5031: 0068 SAR R0

$5032: 0074 RRC R0,2

$5033: 0020 NEGR R0

$5034: 0032 GSWD R2

>

You can clearly see our EIS instruction. Looking back at the listing, the next instruction should be a CALL. The disassembly shows "JSR R5". This is correct: CALL is an alias for JSR R5. What about the rest of this?

If you look in Example 2's source code, you'll see that the CALL was followed by some data:

CALL PRINT.FLS

DECLE 7 ; 7 is the color number for "white"

DECLE $200 + 10*20 + 1

DECLE " Copyright 2007 ", 0

jzIntv's debugger doesn't know that there is data after the CALL instruction, so it assumes it's code when it disassembles it. This gives amusing results such as we saw above. We can verify, however, that the data is what we expect it to be by using the "M" command to display a memory dump.

> m5022 5020: 0021 0000 0002 0004 0150 003D 0007 02C9 # .........P...... 5028: 0020 0020 0043 006F 0070 0079 0072 0069 # .....C.o.p.y.r.i 5030: 0067 0068 0074 0020 0032 0030 0030 0037 # .g.h.t...2.0.0.7 5038: 0020 0020 0000 0220 0001 02A9 02AC 0200 # .............¼.. 5040: 0007 02A9 02AC 02A8 0275 0085 0007 000F # .....¼.¿.u...... 5048: 0006 0049 0071 0200 0006 0338 0020 004C # ...I.q.....8...L 5050: 0048 00C8 0260 02A8 0080 022C 0009 0059 # .H.╚...¿.......Y 5058: 0028 0061 00C7 00AF 02B7 0000 0000 0000 # ...a.╟.».╖...... 5060: 0000 0000 0000 0000 0000 0000 0000 0000 # ................ >

The format of the memory dump is simple. At the left is the starting address. In the middle are hexadecimal values for 8 locations. At the right is an ASCII representation of the data. As you can see, starting on the second row at location $5028, the phrase " Copyright 2007 " is right where we expect it. The extra '.' characters between letters are due to the fact that memory locations are 16-bits wide, but characters are only 8 bits. Additional information could be in those other bits.

Stepping Through

Now let's see what the whole program does. We'll first set a breakpoint at the last instruction, and then tell jzIntv to step to the end.

> b503b

Set breakpoint at $503B

> s

RD a=5022 d=0002 CP-1610 (PC = $5022) t=54475

0000 C0C0 0290 8007 5022 1E87 02f2 5023 ----I--- JSR R5,$503d 54479

RD a=5023 d=0004 CP-1610 (PC = $5023) t=54479

RD a=5024 d=0150 CP-1610 (PC = $5023) t=54479

RD a=5025 d=003D CP-1610 (PC = $5023) t=54479

0000 C0C0 0290 8007 5022 5026 02f2 503D ----I-i- MVI@ R5,R1 54491

RD a=503D d=02A9 CP-1610 (PC = $503D) t=54491

RD a=5026 d=0007 CP-1610 (PC = $503D) t=54491

0000 0007 0290 8007 5022 5027 02f2 503E ----I-i- MVI@ R5,R4 54499

RD a=503E d=02AC CP-1610 (PC = $503E) t=54499

RD a=5027 d=02C9 CP-1610 (PC = $503E) t=54499

0000 0007 0290 8007 02C9 5028 02f2 503F ----I-i- B $5048 54507

RD a=503F d=0200 CP-1610 (PC = $503F) t=54507

RD a=5040 d=0007 CP-1610 (PC = $503F) t=54507

0000 0007 0290 8007 02C9 5028 02f2 5048 ----I-i- CLRC 54516

RD a=5048 d=0006 CP-1610 (PC = $5048) t=54516

0000 0007 0290 8007 02C9 5028 02f2 5049 ----I--- SLL R1 54520

RD a=5049 d=0049 CP-1610 (PC = $5049) t=54520

0000 000E 0290 8007 02C9 5028 02f2 504A ----I--- RRC R1 54526

RD a=504A d=0071 CP-1610 (PC = $504A) t=54526

0000 0007 0290 8007 02C9 5028 02f2 504B ----I--- B $5053 54532

RD a=504B d=0200 CP-1610 (PC = $504B) t=54532

RD a=504C d=0006 CP-1610 (PC = $504B) t=54532

0000 0007 0290 8007 02C9 5028 02f2 5053 ----I-i- MVI@ R5,R0 54541

RD a=5053 d=02A8 CP-1610 (PC = $5053) t=54541

RD a=5028 d=0020 CP-1610 (PC = $5053) t=54541

0020 0007 0290 8007 02C9 5029 02f2 5054 ----I-i- TSTR R0 54549

RD a=5054 d=0080 CP-1610 (PC = $5054) t=54549

0020 0007 0290 8007 02C9 5029 02f2 5055 ----I-i- BNEQ $504d 54555

RD a=5055 d=022C CP-1610 (PC = $5055) t=54555

RD a=5056 d=0009 CP-1610 (PC = $5055) t=54555

0020 0007 0290 8007 02C9 5029 02f2 504D ----I-i- SUBI #$0020,R0 54564

RD a=504D d=0338 CP-1610 (PC = $504D) t=54564

RD a=504E d=0020 CP-1610 (PC = $504D) t=54564

0000 0007 0290 8007 02C9 5029 02f2 504F -C-ZI-i- SLL R0,2 54572

RD a=504F d=004C CP-1610 (PC = $504F) t=54572

0000 0007 0290 8007 02C9 5029 02f2 5050 -C-ZI--- SLL R0 54580

RD a=5050 d=0048 CP-1610 (PC = $5050) t=54580

0000 0007 0290 8007 02C9 5029 02f2 5051 -C-ZI--- ADDR R1,R0 54586

RD a=5051 d=00C8 CP-1610 (PC = $5051) t=54586

0007 0007 0290 8007 02C9 5029 02f2 5052 ----I-i- MVO@ R0,R4 54592

RD a=5052 d=0260 CP-1610 (PC = $5052) t=54592

WR a=02C9 d=0007 CP-1610 (PC = $5052) t=54592

0007 0007 0290 8007 02CA 5029 02f2 5053 ----I--- MVI@ R5,R0 54601

RD a=5029 d=0020 CP-1610 (PC = $5053) t=54601

0020 0007 0290 8007 02CA 502A 02f2 5054 ----I-i- TSTR R0 54609

0020 0007 0290 8007 02CA 502A 02f2 5055 ----I-i- BNEQ $504d 54615

0020 0007 0290 8007 02CA 502A 02f2 504D ----I-i- SUBI #$0020,R0 54624

0000 0007 0290 8007 02CA 502A 02f2 504F -C-ZI-i- SLL R0,2 54632

0000 0007 0290 8007 02CA 502A 02f2 5050 -C-ZI--- SLL R0 54640

0000 0007 0290 8007 02CA 502A 02f2 5051 -C-ZI--- ADDR R1,R0 54646

0007 0007 0290 8007 02CA 502A 02f2 5052 ----I-i- MVO@ R0,R4 54652

WR a=02CA d=0007 CP-1610 (PC = $5052) t=54652

0007 0007 0290 8007 02CB 502A 02f2 5053 ----I--- MVI@ R5,R0 54661

RD a=502A d=0043 CP-1610 (PC = $5053) t=54661

0043 0007 0290 8007 02CB 502B 02f2 5054 ----I-i- TSTR R0 54669

0043 0007 0290 8007 02CB 502B 02f2 5055 ----I-i- BNEQ $504d 54675

0043 0007 0290 8007 02CB 502B 02f2 504D ----I-i- SUBI #$0020,R0 54684

0023 0007 0290 8007 02CB 502B 02f2 504F -C--I-i- SLL R0,2 54692

008C 0007 0290 8007 02CB 502B 02f2 5050 -C--I--- SLL R0 54700

0118 0007 0290 8007 02CB 502B 02f2 5051 -C--I--- ADDR R1,R0 54706

011F 0007 0290 8007 02CB 502B 02f2 5052 ----I-i- MVO@ R0,R4 54712

WR a=02CB d=011F CP-1610 (PC = $5052) t=54712

011F 0007 0290 8007 02CC 502B 02f2 5053 ----I--- MVI@ R5,R0 54721

RD a=502B d=006F CP-1610 (PC = $5053) t=54721

006F 0007 0290 8007 02CC 502C 02f2 5054 ----I-i- TSTR R0 54729

006F 0007 0290 8007 02CC 502C 02f2 5055 ----I-i- BNEQ $504d 54735

006F 0007 0290 8007 02CC 502C 02f2 504D ----I-i- SUBI #$0020,R0 54744

004F 0007 0290 8007 02CC 502C 02f2 504F -C--I-i- SLL R0,2 54752

013C 0007 0290 8007 02CC 502C 02f2 5050 -C--I--- SLL R0 54760

0278 0007 0290 8007 02CC 502C 02f2 5051 -C--I--- ADDR R1,R0 54766

027F 0007 0290 8007 02CC 502C 02f2 5052 ----I-i- MVO@ R0,R4 54772

WR a=02CC d=027F CP-1610 (PC = $5052) t=54772

027F 0007 0290 8007 02CD 502C 02f2 5053 ----I--- MVI@ R5,R0 54781

RD a=502C d=0070 CP-1610 (PC = $5053) t=54781

0070 0007 0290 8007 02CD 502D 02f2 5054 ----I-i- TSTR R0 54789

0070 0007 0290 8007 02CD 502D 02f2 5055 ----I-i- BNEQ $504d 54795

0070 0007 0290 8007 02CD 502D 02f2 504D ----I-i- SUBI #$0020,R0 54804

0050 0007 0290 8007 02CD 502D 02f2 504F -C--I-i- SLL R0,2 54812

0140 0007 0290 8007 02CD 502D 02f2 5050 -C--I--- SLL R0 54820

0280 0007 0290 8007 02CD 502D 02f2 5051 -C--I--- ADDR R1,R0 54826

0287 0007 0290 8007 02CD 502D 02f2 5052 ----I-i- MVO@ R0,R4 54832

WR a=02CD d=0287 CP-1610 (PC = $5052) t=54832

0287 0007 0290 8007 02CE 502D 02f2 5053 ----I--- MVI@ R5,R0 54841

RD a=502D d=0079 CP-1610 (PC = $5053) t=54841

0079 0007 0290 8007 02CE 502E 02f2 5054 ----I-i- TSTR R0 54849

0079 0007 0290 8007 02CE 502E 02f2 5055 ----I-i- BNEQ $504d 54855

0079 0007 0290 8007 02CE 502E 02f2 504D ----I-i- SUBI #$0020,R0 54864

0059 0007 0290 8007 02CE 502E 02f2 504F -C--I-i- SLL R0,2 54872

0164 0007 0290 8007 02CE 502E 02f2 5050 -C--I--- SLL R0 54880

02C8 0007 0290 8007 02CE 502E 02f2 5051 -C--I--- ADDR R1,R0 54886

02CF 0007 0290 8007 02CE 502E 02f2 5052 ----I-i- MVO@ R0,R4 54892

WR a=02CE d=02CF CP-1610 (PC = $5052) t=54892

02CF 0007 0290 8007 02CF 502E 02f2 5053 ----I--- MVI@ R5,R0 54901

RD a=502E d=0072 CP-1610 (PC = $5053) t=54901

0072 0007 0290 8007 02CF 502F 02f2 5054 ----I-i- TSTR R0 54909

0072 0007 0290 8007 02CF 502F 02f2 5055 ----I-i- BNEQ $504d 54915

0072 0007 0290 8007 02CF 502F 02f2 504D ----I-i- SUBI #$0020,R0 54924

0052 0007 0290 8007 02CF 502F 02f2 504F -C--I-i- SLL R0,2 54932

0148 0007 0290 8007 02CF 502F 02f2 5050 -C--I--- SLL R0 54940

0290 0007 0290 8007 02CF 502F 02f2 5051 -C--I--- ADDR R1,R0 54946

0297 0007 0290 8007 02CF 502F 02f2 5052 ----I-i- MVO@ R0,R4 54952

WR a=02CF d=0297 CP-1610 (PC = $5052) t=54952

0297 0007 0290 8007 02D0 502F 02f2 5053 ----I--- MVI@ R5,R0 54961

RD a=502F d=0069 CP-1610 (PC = $5053) t=54961

0069 0007 0290 8007 02D0 5030 02f2 5054 ----I-i- TSTR R0 54969

0069 0007 0290 8007 02D0 5030 02f2 5055 ----I-i- BNEQ $504d 54975

0069 0007 0290 8007 02D0 5030 02f2 504D ----I-i- SUBI #$0020,R0 54984

0049 0007 0290 8007 02D0 5030 02f2 504F -C--I-i- SLL R0,2 54992

0124 0007 0290 8007 02D0 5030 02f2 5050 -C--I--- SLL R0 55000

0248 0007 0290 8007 02D0 5030 02f2 5051 -C--I--- ADDR R1,R0 55006

024F 0007 0290 8007 02D0 5030 02f2 5052 ----I-i- MVO@ R0,R4 55012

WR a=02D0 d=024F CP-1610 (PC = $5052) t=55012

024F 0007 0290 8007 02D1 5030 02f2 5053 ----I--- MVI@ R5,R0 55021

RD a=5030 d=0067 CP-1610 (PC = $5053) t=55021

0067 0007 0290 8007 02D1 5031 02f2 5054 ----I-i- TSTR R0 55029

0067 0007 0290 8007 02D1 5031 02f2 5055 ----I-i- BNEQ $504d 55035

0067 0007 0290 8007 02D1 5031 02f2 504D ----I-i- SUBI #$0020,R0 55044

0047 0007 0290 8007 02D1 5031 02f2 504F -C--I-i- SLL R0,2 55052

011C 0007 0290 8007 02D1 5031 02f2 5050 -C--I--- SLL R0 55060

0238 0007 0290 8007 02D1 5031 02f2 5051 -C--I--- ADDR R1,R0 55066

023F 0007 0290 8007 02D1 5031 02f2 5052 ----I-i- MVO@ R0,R4 55072

WR a=02D1 d=023F CP-1610 (PC = $5052) t=55072

023F 0007 0290 8007 02D2 5031 02f2 5053 ----I--- MVI@ R5,R0 55081

RD a=5031 d=0068 CP-1610 (PC = $5053) t=55081

0068 0007 0290 8007 02D2 5032 02f2 5054 ----I-i- TSTR R0 55089

0068 0007 0290 8007 02D2 5032 02f2 5055 ----I-i- BNEQ $504d 55095

0068 0007 0290 8007 02D2 5032 02f2 504D ----I-i- SUBI #$0020,R0 55104

0048 0007 0290 8007 02D2 5032 02f2 504F -C--I-i- SLL R0,2 55112

0120 0007 0290 8007 02D2 5032 02f2 5050 -C--I--- SLL R0 55120

0240 0007 0290 8007 02D2 5032 02f2 5051 -C--I--- ADDR R1,R0 55126

0247 0007 0290 8007 02D2 5032 02f2 5052 ----I-i- MVO@ R0,R4 55132

WR a=02D2 d=0247 CP-1610 (PC = $5052) t=55132

0247 0007 0290 8007 02D3 5032 02f2 5053 ----I--- MVI@ R5,R0 55141

RD a=5032 d=0074 CP-1610 (PC = $5053) t=55141

0074 0007 0290 8007 02D3 5033 02f2 5054 ----I-i- TSTR R0 55149

0074 0007 0290 8007 02D3 5033 02f2 5055 ----I-i- BNEQ $504d 55155

0074 0007 0290 8007 02D3 5033 02f2 504D ----I-i- SUBI #$0020,R0 55164

0054 0007 0290 8007 02D3 5033 02f2 504F -C--I-i- SLL R0,2 55172

0150 0007 0290 8007 02D3 5033 02f2 5050 -C--I--- SLL R0 55180

02A0 0007 0290 8007 02D3 5033 02f2 5051 -C--I--- ADDR R1,R0 55186

02A7 0007 0290 8007 02D3 5033 02f2 5052 ----I-i- MVO@ R0,R4 55192

WR a=02D3 d=02A7 CP-1610 (PC = $5052) t=55192

02A7 0007 0290 8007 02D4 5033 02f2 5053 ----I--- MVI@ R5,R0 55201

RD a=5033 d=0020 CP-1610 (PC = $5053) t=55201

0020 0007 0290 8007 02D4 5034 02f2 5054 ----I-i- TSTR R0 55209

0020 0007 0290 8007 02D4 5034 02f2 5055 ----I-i- BNEQ $504d 55215

0020 0007 0290 8007 02D4 5034 02f2 504D ----I-i- SUBI #$0020,R0 55224

0000 0007 0290 8007 02D4 5034 02f2 504F -C-ZI-i- SLL R0,2 55232

0000 0007 0290 8007 02D4 5034 02f2 5050 -C-ZI--- SLL R0 55240

0000 0007 0290 8007 02D4 5034 02f2 5051 -C-ZI--- ADDR R1,R0 55246

0007 0007 0290 8007 02D4 5034 02f2 5052 ----I-i- MVO@ R0,R4 55252

WR a=02D4 d=0007 CP-1610 (PC = $5052) t=55252

0007 0007 0290 8007 02D5 5034 02f2 5053 ----I--- MVI@ R5,R0 55261

RD a=5034 d=0032 CP-1610 (PC = $5053) t=55261

0032 0007 0290 8007 02D5 5035 02f2 5054 ----I-i- TSTR R0 55269

0032 0007 0290 8007 02D5 5035 02f2 5055 ----I-i- BNEQ $504d 55275

0032 0007 0290 8007 02D5 5035 02f2 504D ----I-i- SUBI #$0020,R0 55284

0012 0007 0290 8007 02D5 5035 02f2 504F -C--I-i- SLL R0,2 55292

0048 0007 0290 8007 02D5 5035 02f2 5050 -C--I--- SLL R0 55300

0090 0007 0290 8007 02D5 5035 02f2 5051 -C--I--- ADDR R1,R0 55306

0097 0007 0290 8007 02D5 5035 02f2 5052 ----I-i- MVO@ R0,R4 55312

WR a=02D5 d=0097 CP-1610 (PC = $5052) t=55312

0097 0007 0290 8007 02D6 5035 02f2 5053 ----I--- MVI@ R5,R0 55321

RD a=5035 d=0030 CP-1610 (PC = $5053) t=55321

0030 0007 0290 8007 02D6 5036 02f2 5054 ----I-i- TSTR R0 55329

0030 0007 0290 8007 02D6 5036 02f2 5055 ----I-i- BNEQ $504d 55335

0030 0007 0290 8007 02D6 5036 02f2 504D ----I-i- SUBI #$0020,R0 55344

0010 0007 0290 8007 02D6 5036 02f2 504F -C--I-i- SLL R0,2 55352

0040 0007 0290 8007 02D6 5036 02f2 5050 -C--I--- SLL R0 55360

0080 0007 0290 8007 02D6 5036 02f2 5051 -C--I--- ADDR R1,R0 55366

0087 0007 0290 8007 02D6 5036 02f2 5052 ----I-i- MVO@ R0,R4 55372

WR a=02D6 d=0087 CP-1610 (PC = $5052) t=55372

0087 0007 0290 8007 02D7 5036 02f2 5053 ----I--- MVI@ R5,R0 55381

RD a=5036 d=0030 CP-1610 (PC = $5053) t=55381

0030 0007 0290 8007 02D7 5037 02f2 5054 ----I-i- TSTR R0 55389

0030 0007 0290 8007 02D7 5037 02f2 5055 ----I-i- BNEQ $504d 55395

0030 0007 0290 8007 02D7 5037 02f2 504D ----I-i- SUBI #$0020,R0 55404

0010 0007 0290 8007 02D7 5037 02f2 504F -C--I-i- SLL R0,2 55412

0040 0007 0290 8007 02D7 5037 02f2 5050 -C--I--- SLL R0 55420

0080 0007 0290 8007 02D7 5037 02f2 5051 -C--I--- ADDR R1,R0 55426

0087 0007 0290 8007 02D7 5037 02f2 5052 ----I-i- MVO@ R0,R4 55432

WR a=02D7 d=0087 CP-1610 (PC = $5052) t=55432

0087 0007 0290 8007 02D8 5037 02f2 5053 ----I--- MVI@ R5,R0 55441

RD a=5037 d=0037 CP-1610 (PC = $5053) t=55441

0037 0007 0290 8007 02D8 5038 02f2 5054 ----I-i- TSTR R0 55449

0037 0007 0290 8007 02D8 5038 02f2 5055 ----I-i- BNEQ $504d 55455

0037 0007 0290 8007 02D8 5038 02f2 504D ----I-i- SUBI #$0020,R0 55464

0017 0007 0290 8007 02D8 5038 02f2 504F -C--I-i- SLL R0,2 55472

005C 0007 0290 8007 02D8 5038 02f2 5050 -C--I--- SLL R0 55480

00B8 0007 0290 8007 02D8 5038 02f2 5051 -C--I--- ADDR R1,R0 55486

00BF 0007 0290 8007 02D8 5038 02f2 5052 ----I-i- MVO@ R0,R4 55492

WR a=02D8 d=00BF CP-1610 (PC = $5052) t=55492

00BF 0007 0290 8007 02D9 5038 02f2 5053 ----I--- MVI@ R5,R0 55501

RD a=5038 d=0020 CP-1610 (PC = $5053) t=55501

0020 0007 0290 8007 02D9 5039 02f2 5054 ----I-i- TSTR R0 55509

0020 0007 0290 8007 02D9 5039 02f2 5055 ----I-i- BNEQ $504d 55515

0020 0007 0290 8007 02D9 5039 02f2 504D ----I-i- SUBI #$0020,R0 55524

0000 0007 0290 8007 02D9 5039 02f2 504F -C-ZI-i- SLL R0,2 55532

0000 0007 0290 8007 02D9 5039 02f2 5050 -C-ZI--- SLL R0 55540

0000 0007 0290 8007 02D9 5039 02f2 5051 -C-ZI--- ADDR R1,R0 55546

0007 0007 0290 8007 02D9 5039 02f2 5052 ----I-i- MVO@ R0,R4 55552

WR a=02D9 d=0007 CP-1610 (PC = $5052) t=55552

0007 0007 0290 8007 02DA 5039 02f2 5053 ----I--- MVI@ R5,R0 55561

RD a=5039 d=0020 CP-1610 (PC = $5053) t=55561

0020 0007 0290 8007 02DA 503A 02f2 5054 ----I-i- TSTR R0 55569

0020 0007 0290 8007 02DA 503A 02f2 5055 ----I-i- BNEQ $504d 55575

0020 0007 0290 8007 02DA 503A 02f2 504D ----I-i- SUBI #$0020,R0 55584

0000 0007 0290 8007 02DA 503A 02f2 504F -C-ZI-i- SLL R0,2 55592

0000 0007 0290 8007 02DA 503A 02f2 5050 -C-ZI--- SLL R0 55600

0000 0007 0290 8007 02DA 503A 02f2 5051 -C-ZI--- ADDR R1,R0 55606

0007 0007 0290 8007 02DA 503A 02f2 5052 ----I-i- MVO@ R0,R4 55612

WR a=02DA d=0007 CP-1610 (PC = $5052) t=55612

0007 0007 0290 8007 02DB 503A 02f2 5053 ----I--- MVI@ R5,R0 55621

RD a=503A d=0000 CP-1610 (PC = $5053) t=55621

0000 0007 0290 8007 02DB 503B 02f2 5054 ----I-i- TSTR R0 55629

0000 0007 0290 8007 02DB 503B 02f2 5055 ---ZI-i- BNEQ $504d 55635

0000 0007 0290 8007 02DB 503B 02f2 5057 ---ZI-i- SLLC R1 55642

RD a=5057 d=0059 CP-1610 (PC = $5057) t=55642

0000 000E 0290 8007 02DB 503B 02f2 5058 ----I--- ADCR R0 55648

RD a=5058 d=0028 CP-1610 (PC = $5058) t=55648

0000 000E 0290 8007 02DB 503B 02f2 5059 ---ZI-i- SLR R1 55654

RD a=5059 d=0061 CP-1610 (PC = $5059) t=55654

0000 0007 0290 8007 02DB 503B 02f2 505A ----I--- ADDR R0,R7 55660

RD a=505A d=00C7 CP-1610 (PC = $505A) t=55660

0000 0007 0290 8007 02DB 503B 02f2 505B ----I-i- MOVR R5,R7 55667

RD a=505B d=00AF CP-1610 (PC = $505B) t=55667

0000 0007 0290 8007 02DB 503B 02f2 503B ----I-i- B $503b 55674

Hit breakpoint at $503B

0000 0007 0290 8007 02DB 503B 02f2 503B ----I-i- B $503b 55674

>

Wrapping Up

That concludes the quick tour of the most useful commands in jzIntv's debugger. You can quit the debugger by giving it the "Q" command. You're encouraged at this point to try single-stepping through other programs to see how the instructions work. The next tutorial aims at introducing the various families of instructions.