Cartridge Port

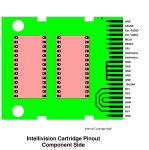

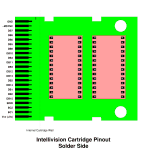

The Master Component's cartridge port consists of a single 44-pin 0.1" spacing edge-card connector. A number of essential bus signals are brought out on this connector. The following figures illustrate which of these signals corresponds to each of the various cartridge pins. The table afterwards lists what each signal does.

Pin Mapping on Intellivision Cartridge Port

Pin Assignments

| Component Side (Top) | Solder Side (Bottom) | |||||

|---|---|---|---|---|---|---|

| Description | Name | Pin | Pin | Name | Description | |

| Intellivision I: Ground | GND | 2 | 1 | GND | Ground. | |

| Intellivison II: System Changer External Video | Ext. VIDEO | |||||

| Character BLaNK | CBLNK | 4 | 3 | ~MSYNC | Master SYNC. | |

| External Audio Input. | Ext. AUDIO | 6 | 5 | DB7 | Bit 7 of the Address / Data Bus. | |

| External Video Input. (Intellivision I only) | Ext. VIDEO | 8 | 7 | DB8 | Bit 8 of the Address / Data Bus. | |

| Master CLocK. | MCLK | 10 | 9 | DB6 | Bit 6 of the Address / Data Bus. | |

| Reset input. | RESET | 12 | 11 | DB9 | Bit 9 of the Address / Data Bus. | |

| Timing signal from the STIC. | SR1 | 14 | 13 | DB5 | Bit 5 of the Address / Data Bus. | |

| Intellivoice special purpose. | ??? | 16 | 15 | DB10 | Bit 10 of the Address / Data Bus. | |

| ??? | 18 | 17 | DB4 | Bit 4 of the Address / Data Bus. | ||

| Ground | GND | 20 | 19 | DB11 | Bit 11 of the Address / Data Bus. | |

| GND | 22 | 21 | DB3 | Bit 3 of the Address / Data Bus. | ||

| GND | 24 | 23 | DB12 | Bit 12 of the Address / Data Bus. | ||

| GND | 26 | 25 | DB13 | Bit 13 of the Address / Data Bus. | ||

| GND | 28 | 27 | DB2 | Bit 2 of the Address / Data Bus. | ||

| BUS AcKnowledge. | ~BUSAK | 30 | 29 | DB14 | Bit 14 of the Address / Data Bus. | |

| This is an input. This BC1 drives the EXEC ROMs, the PSG, and the 8-bit RAMs. | BC1 | 32 | 31 | DB1 | Bit 1 of the Address / Data Bus. | |

| This is an input. This BC2 drives the EXEC ROMs, the PSG, and the 8-bit RAMs. | BC2 | 34 | 33 | DB0 | Bit 0 of the Address / Data Bus. | |

| This is an input. This BDIR drives the EXEC ROMs, the PSG, and the 8-bit RAMs. | BDIR | 36 | 35 | DB15 | Bit 15 of the Address / Data Bus. | |

| This is an output. This BDIR is usually looped back by the cartridge on pin 36. | BDIR | 38 | 37 | BDIR | This is an output. This BDIR usually provides the current bus phase to the cartridge ROMs. | |

| This is an output. This BC2 is usually looped back by the cartridge on pin 34. | BC2 | 40 | 39 | BC2 | This is an output. This BC2 usually provides the current bus phase to the cartridge ROMs. | |

| This is an output. This BC1 is usually looped back by the cartridge on pin 32. | BC1 | 42 | 41 | BC1 | This is an output. This BC1 usually provides the current bus phase to the cartridge ROMs. | |

| Ground | GND | 44 | 43 | Vcc | +5v power. | |

The following meanings are assigned to the cartridge port signals:

- Vcc -- +5v Power

- GND -- Ground

- RESET -- System Reset

Pulling this line low will send a short reset pulse to the STIC. This will result in ~MSYNC being brought low by the STIC, thereby resetting the machine. The signal is capacitively coupled inside the Intellivision. Thus, the Intellivision will only respond to the high-to-low transition of the pulse. Holding this line low will not hold the Intellivision in reset.

- ~MSYNC -- Master Sync

This signal goes low for at least 10ms during Reset. It is generated by the STIC as soon as the STIC recognizes a low pulse on its RESET line.

- MCLK -- Master Clock

This pin provides the 3.579545MHz master clock signal that drives the Master Component.

- BC1, BC2, BDIR -- Bus Control

These are the bus control signals as described in the CPU sections above. The outputs on pins 38, 40, and 42 come directly from the INTAK remapping circuitry. Cartridges generally loop these signals back on pins 36, 34, and 32. The outputs on pins 37, 39, and 41 are also directly connected to the INTAK remapping circuitry, and are the signals that most Mattel cartridges use for determining the bus phaase.

- DB0 thru DB15 -- Address/Data Bus

This is the 16-bit multiplexed address/data bus.

- ~BUSAK -- BUS AcKnowledge

This signal goes low when the CPU has relinquished the bus during a DMA access by the STIC. It appears possible that external devices can access the PSG, EXEC, and 8-bit RAM during the time ~BUSAK is low, but it's unclear whether this is the case. In all likelihood, it is not the case.

- SR1 -- STIC Timing Signal

This signal is tied to the CPU's ~INTRM input, triggering an interrupt when the STIC goes into the vertical refresh phase.

- CBLNK -- "Character BLaNK" / Horizontal Retrace

Used for genlocking the Keyboard Component's TMS9927 to the Master Component's AY8900 STIC.

- EXT AUDIO -- External Audio Input

The Intellivoice and ECS's second Programmable Sound Generator provide audio input via this pin. I'd imagine if the Keyboard Component can generate Audio, it also provides it on this pin.

- EXT VIDEO -- External Video Input

This was originally designed to accept the genlocked video from the Keyboard Component. The Intellivision II changed the external video input circuit slightly to accept the non-genlocked video from the System Changer. It also moved this to pin 2, which was previously a ground input.

- ??? -- Intellivoice Speech ROM Expansion Bus

These pins are tied to ground on non-Intellivoice cartridges, and left open on Intellivoice-aware cartridges.

(TODO: These lines, along with a third one on pin 20 I think, are connected to the Intellivoice's 3-wire serial bus for speech-ROM expansion. I need to look up the exact assignment of these signals. --Mr z 19:12, 12 Jan 2005 (EST))