Introducing the Instruction Set Part 4

This short tutorial examines the shift instructions. If you haven't read Part 1 or Part 2 yet, you might consider doing so first.

Contents

Shift and Rotate Instructions

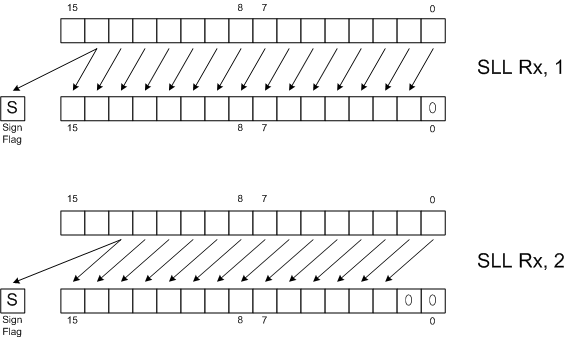

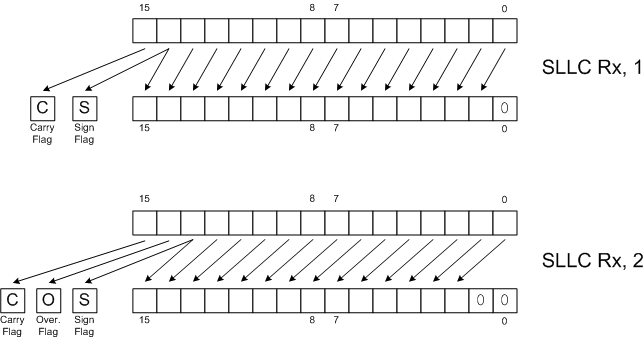

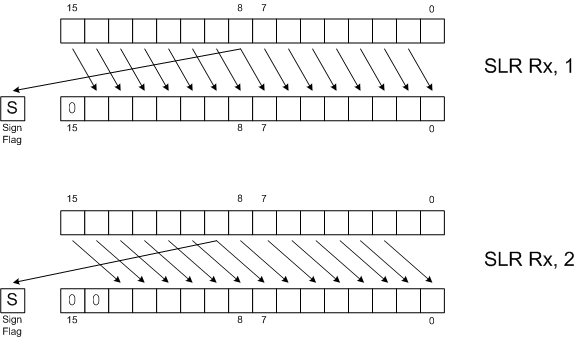

The CP1610 offers a rich variety of shift and rotate instructions. These are useful for bit manipulation and certain types of mathematics. Shifting left by one position is equivalent to multiplying by 2. Shifting right by one position is roughly equivalent to dividing by 2. The shift instructions only operate on R0 through R3. You cannot use them with R4 through R7. Overall, CP-1600 offers 8 separate shift instructions. Each can shift by one or two positions.

Click on a given mnemonic to see how it operates.

| SLL Rx[, 2] | Shift Logical Left |

|---|---|

| SLR Rx[, 2] | Shift Logical Right |

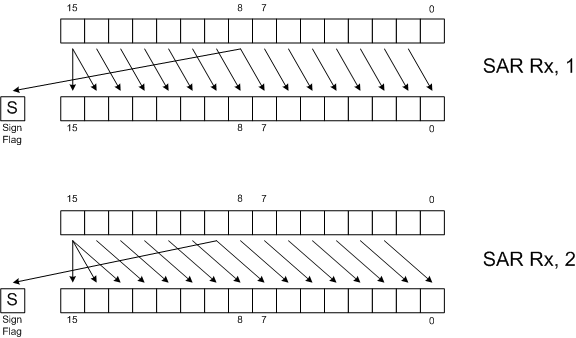

| SAR Rx[, 2] | Shift Arithmetic Right |

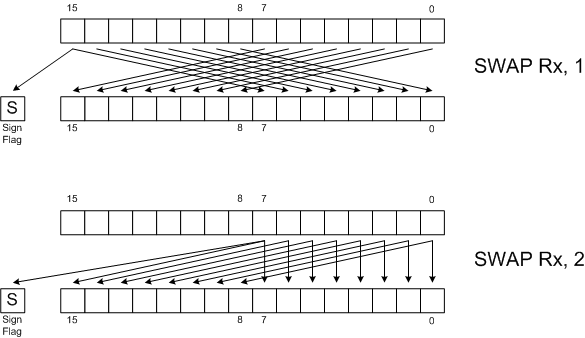

| SWAP Rx[, 2] | Swap bytes |

| SLLC Rx[, 2] | SLL into Carry |

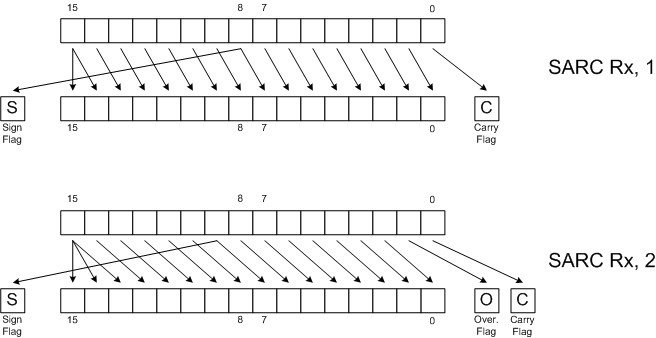

| SARC Rx[, 2] | SAR into Carry |

| RLC Rx[, 2] | Rotate Left thru Carry |

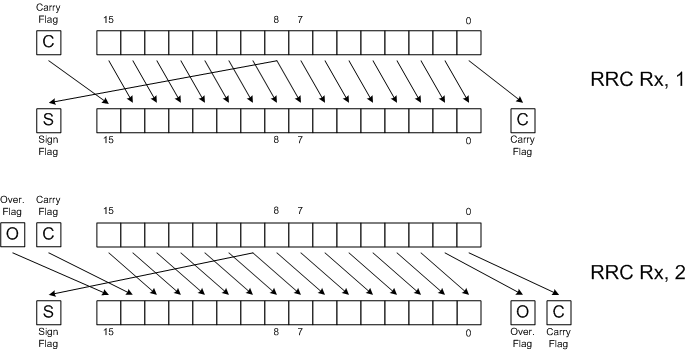

| RRC Rx[, 2] | Rotate Right thru Carry |

Logical shifts (SLL, SLR, SLLC) fill the newly-opened positions with zeros. Arithmetic shifts (SAR, SARC) fill the newly opened positions with copies of bit 15. Logical right shifts can be thought of as "unsigned divide by 2", whereas arithmetic right shifts can be thought of as "signed divide by 2, rounding toward negative."

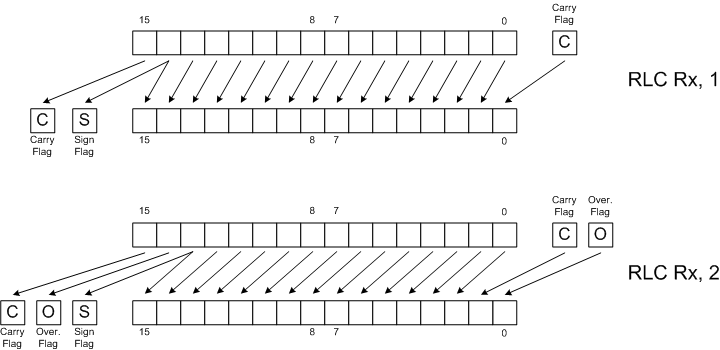

Rotates are like shifts, except that they fill the vacated bits with bits from a status register. By itself, this property has no particular mathematical meaning. When rotates combine with shifts, though, they can perform extended-precision operations.

Shift and Rotate Illustrations

The following diagrams illustrate the behavior of each of the 8 shift and rotate instructions.

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

<BR\>

Caveats

Shift instructions are Non-interruptible Instructions. Be sure to include an interruptible instruction in a long sequence of shifts or other non-interruptible instructions, otherwise you could cause display glitches.

Using Shifts for Multiplication

Shifting values left multiplies them by powers of two. Each bit position shifted corresponds to another power of two. Shifting left one position multiplies by 2; shifting by two positions multiplies by 4. The following table illustrates the relationship between positions shifted and the power of two. The table stops at 8 for brevity's sake.

| Number of positions shifted left | Power of 2 multiplied by | Example Code Sequence |

|---|---|---|

| 1 | 2 | |

| 2 | 4 | |

| 3 | 8 | |

| 4 | 16 | |

| 5 | 32 | |

| 6 | 64 | |

| 7 | 128 | |

| 8 | 256 | |

You can combine shift and add instructions to perform simple multiplications by constants that aren't powers of two. The following example shows how to multiply the value in R0 by 20, using R1 as a temporary variable.

SLL R0, 2 ; Multiply R0 by 4

MOVR R0, R1 ; Save a copy of original value * 4

SLL R0, 2 ; Multiply R0 by 4 again (original value * 16)

ADDR R1, R0 ; Add (value * 4) to (value * 16), giving (value * 20)

Using Shifts for Division by Powers of Two

Right shifts divide by powers of two, by default truncating the fractional portion. This is the same as rounding towards negative. With a minor tweak, the same code can round upwards. The following table shows example code sequences for various power-of-two divides on signed numbers and unsigned numbers.

| Number of positions shifted right | Power of 2 divided by | Example Code Sequence for signed, rounding to negative | Example Code Sequence for signed, rounding to positive | Example Code Sequence for unsigned, rounding to negative | Example Code Sequence for unsigned, rounding to positive |

|---|---|---|---|---|---|

| 1 | 2 | |

|

|

|

| 2 | 4 | |

|

|

|

| 3 | 8 | |

|

|

|

| 4 | 16 | |

|

|

|

| 5 | 32 | |

|

|

|

| 6 | 64 | |

|

|

|

| 7 | 128 | |

|

|

|

| 8 | 256 | |

|

|

|

Combining Shifts and Rotates for Extended-Precision Shifts

Rotate instructions combined with shift instructions make it easy to shift values longer than 16 bits. The following examples show how to shift the 32 bit number held in R1:R0 left and right by 1 and 2 positions. (R1 holds bits 16..31 of the 32-bit number.)

; Shift R1:R0 left by 1 position

SLLC R0, 1 ; Shift lower half left, extra bit to 'C'

RLC R1, 1 ; Shift upper half left, pulling lower bit from 'C'

; Shift R1:R0 left by 2 positions

SLLC R0, 2 ; Shift lower half left, extra bits to 'C', 'O'

RLC R1, 2 ; Shift upper half left, pulling lower bit from 'C', 'O'

; Shift R1:R0 right by 1 position (arithmetic right shift)

SARC R1, 1 ; Shift upper half left, extra bit to 'C'

RRC R0, 1 ; Shift lower half left, pulling lower bit from 'C'

; Shift R1:R0 left by 2 positions (arithmetic right shift)

SARC R1, 2 ; Shift upper half right, extra bits to 'C', 'O'

RRC R0, 2 ; Shift lower half right, pulling lower bit from 'C', 'O'

Moving On

At this point, you may wish to continue with the remaining parts of this tutorial:

- Introducing the Instruction Set Part 1: The CPU, Memory and Registers; Primary Instructions and Addressing Modes

- Introducing the Instruction Set Part 2: Single Register and Implied Operand Instructions

- Introducing the Instruction Set Part 4: Branches, Conditional Branches and Calls

Or, you can return to the Programming Tutorials index.